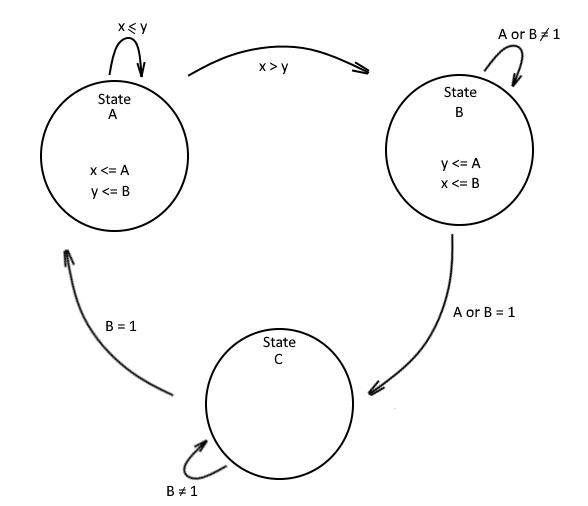

finite state machine

FSM – finite state machine

FSM, bir vhdl kodlama metodudur.

NSL next state machine decide which state to go under what conditions state’e karar verme. OFL output function logic what to do in what state under what conditions state altinda ne yapilacagina karar verme.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity finite_state_machine is

port(

A: in std_logic;

B: in std_logic;

clock_signal: in std_logic

);

end finite_state_machine;

architecture finite_state_machine_a of finite_state_machine is

signal x : std_logic;

signal y : std_logic;

constant state_a : std_logic_vector(2 downto 0) := "001";

constant state_b : std_logic_vector(2 downto 0) := "010";

constant state_c : std_logic_vector(2 downto 0) := "100";

signal state : std_logic_vector(2 downto 0) := "001";

begin

process (clock_signal)

begin

if rising_edge(clock_signal) then

case state is

when state_a =>

x <= A;

y <= B;

if (x <= y) then -- --|

state <= state_a; -- |

else -- | NSL

state <= state_b; -- |

end if; -- --|

when state_b =>

y <= A;

x <= B;

if ( (A or B) = '1' ) then -- --|

state <= state_c; -- |

else -- | NSL

state <= state_b; -- |

end if; -- --|

when state_c =>

-- do nothing

if (B = '1') then -- --|

state <= state_a; -- |

else -- | NSL

state <= state_c; -- |

end if; -- --|

when others => state <= state;

end case;

end if;

end process;

end finite_state_machine_a;

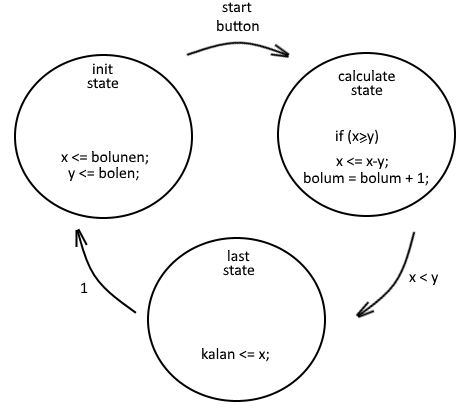

Divider

Asagidaki kod simülasyona geçiyor ama orada simülasyon yapilamiyor. Galiba sorun bolunen ve bolum signallerinin degisken olarak tanitilmamasi.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use ieee.std_logic_signed.all;

entity divider is

port(

bolunen : in std_logic_vector(2 downto 0);

bolen : in std_logic_vector(2 downto 0);

start_button : in std_logic;

clock_signal : in std_logic;

kalan : out std_logic_vector(2 downto 0);

bolum : inout std_logic_vector(2 downto 0)

);

end divider;

architecture divider_a of divider is

signal x: std_logic_vector(2 downto 0);

signal y: std_logic_vector(2 downto 0);

constant init_state : std_logic_vector(2 downto 0) := "001";

constant calculate_state : std_logic_vector(2 downto 0) := "010";

constant last_state : std_logic_vector(2 downto 0) := "100";

signal state : std_logic_vector(2 downto 0) := "001";

begin

process(clock_signal)

begin

if rising_edge(clock_signal) then

case state is

when init_state =>

x <= bolunen;

y <= bolen;

if (start_button = '1') then

state <= calculate_state;

else

state <= init_state;

end if;

when calculate_state =>

if (x >= y) then

x <= x-y;

bolum <= bolum + 1;

end if;

if (x < y) then

state <= last_state;

else

state <= calculate_state;

end if;

when last_state =>

kalan <= x;

state <= init_state;

when others =>

state <= init_state;

end case;

end if;

end process;

end divider_a;

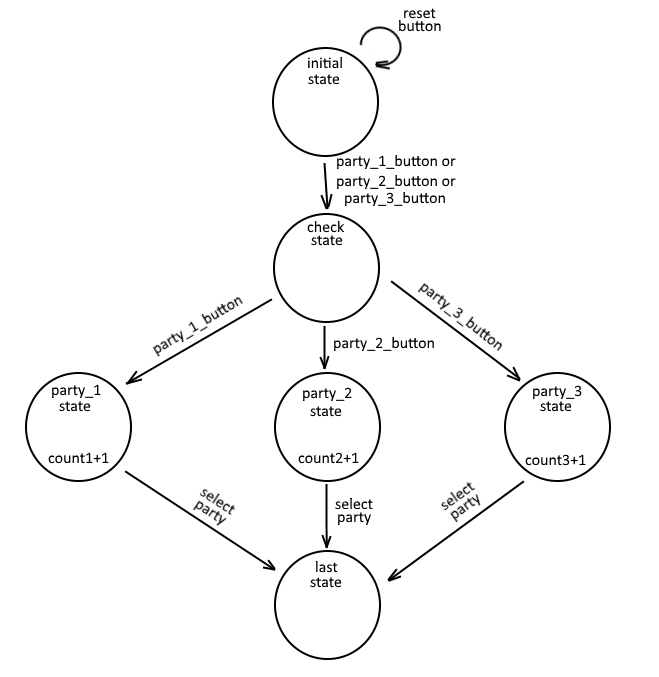

Voting machine

button basmalarinda en az 2 clock cycle beklemek gerekli. Select_party butonuna da party button’larindan hemen sonra hic beklemeden basmak gerekiyor.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_arith.ALL;

use IEEE.STD_LOGIC_unsigned.ALL;

entity voting_machine is

port(

clock_signal: in std_logic;

reset_button: in std_logic;

party_1_button: in std_logic;

party_2_button: in std_logic;

party_3_button: in std_logic;

select_party: in std_logic;

count_1_output: out std_logic_vector(5 downto 0);

count_2_output: out std_logic_vector(5 downto 0);

count_3_output: out std_logic_vector(5 downto 0)

);

end voting_machine;

architecture voting_machine_a of voting_machine is

signal count_1: std_logic_vector(5 downto 0);

signal count_2: std_logic_vector(5 downto 0);

signal count_3: std_logic_vector(5 downto 0);

signal state: std_logic_vector(5 downto 0);

constant initial_state: std_logic_vector(5 downto 0) := "000001";

constant check_state: std_logic_vector(5 downto 0) := "000010";

constant party_1_state: std_logic_vector(5 downto 0) := "000100";

constant party_2_state: std_logic_vector(5 downto 0) := "001000";

constant party_3_state: std_logic_vector(5 downto 0) := "010000";

constant last_state: std_logic_vector(5 downto 0) := "100000";

begin

process(clock_signal, reset_button, party_1_button, party_2_button, party_3_button)

begin

if (reset_button = '1') then

count_1 <= (others => '0');

count_2 <= (others => '0');

count_3 <= (others => '0');

else

if rising_edge(clock_signal) then

case state is

when initial_state =>

if (party_1_button = '1' or party_2_button = '1' or party_3_button = '1') then

state <= check_state;

else

state <= initial_state;

end if;

when check_state =>

if party_1_button='1' then

state <= party_1_state;

elsif party_2_button = '1' then

state <= party_2_state;

elsif party_3_button = '1' then

state <= party_3_state;

else

state <= check_state;

end if;

when party_1_state =>

count_1 <= count_1 + 1;

if select_party = '1' then

state <= last_state;

else

state <= party_1_state;

end if;

when party_2_state =>

count_2 <= count_2 + 1;

if select_party = '1' then

state <= last_state;

else

state <= party_2_state;

end if;

when party_3_state =>

count_3 <= count_3 + 1;

if select_party = '1' then

state <= last_state;

else

state <= party_3_state;

end if;

when last_state =>

state <= initial_state;

when others =>

state <= initial_state;

end case;

end if; -- if rising_edge(clock_signal) then

end if; -- if (reset_button = '1') then

end process;

count_1_output <= count_1;

count_2_output <= count_2;

count_3_output <= count_3;

end voting_machine_a;

voting machine simulaston kodlari :

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY voting_machine_sim IS

END voting_machine_sim;

ARCHITECTURE behavior OF voting_machine_sim IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT voting_machine

PORT(

clock_signal : IN std_logic;

reset_button : IN std_logic;

party_1_button : IN std_logic;

party_2_button : IN std_logic;

party_3_button : IN std_logic;

select_party : IN std_logic;

count_1_output : OUT std_logic_vector(5 downto 0);

count_2_output : OUT std_logic_vector(5 downto 0);

count_3_output : OUT std_logic_vector(5 downto 0)

);

END COMPONENT;

--Inputs

signal clock_signal : std_logic := '0';

signal reset_button : std_logic := '0';

signal party_1_button : std_logic := '0';

signal party_2_button : std_logic := '0';

signal party_3_button : std_logic := '0';

signal select_party : std_logic := '0';

--Outputs

signal count_1_output : std_logic_vector(5 downto 0);

signal count_2_output : std_logic_vector(5 downto 0);

signal count_3_output : std_logic_vector(5 downto 0);

-- Clock period definitions

constant clock_signal_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: voting_machine PORT MAP (

clock_signal => clock_signal,

reset_button => reset_button,

party_1_button => party_1_button,

party_2_button => party_2_button,

party_3_button => party_3_button,

select_party => select_party,

count_1_output => count_1_output,

count_2_output => count_2_output,

count_3_output => count_3_output

);

-- Clock process definitions

clock_signal_process :process

begin

clock_signal <= '0';

wait for clock_signal_period/2;

clock_signal <= '1';

wait for clock_signal_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

wait for 100 ns;

-- reset button high for 2 cycle

reset_button <= '1';

wait for clock_signal_period*2;

reset_button <= '0';

-- button init to low

party_1_button <= '0';

party_2_button <= '0';

party_3_button <= '0';

wait for clock_signal_period*2;

-- party_1_button high for 2 cycle

party_1_button <= '1';

wait for clock_signal_period*2;

party_1_button <= '0';

-- select_party button high for 2 cycle

select_party <= '1';

wait for clock_signal_period*2;

select_party <= '0';

------------------------------------------

-- party_1 counter must be 1 at that point

------------------------------------------

-- party_3_button high for 2 cycle

party_3_button <= '1';

wait for clock_signal_period*2;

party_3_button <= '0';

-- select_party button high for 2 cycle

select_party <= '1';

wait for clock_signal_period*2;

select_party <= '0';

------------------------------------------

-- party_3 counter must be 1 at that point

------------------------------------------

-- party_3_button high for 2 cycle

party_3_button <= '1';

wait for clock_signal_period*2;

party_3_button <= '0';

-- select_party button high for 2 cycle

select_party <= '1';

wait for clock_signal_period*2;

select_party <= '0';

------------------------------------------

-- party_3 counter must be 2 at that point

------------------------------------------

-- party_2_button high for 2 cycle

party_2_button <= '1';

wait for clock_signal_period*2;

party_2_button <= '0';

-- select_party button high for 2 cwycle

select_party <= '1';

wait for clock_signal_period*2;

select_party <= '0';

------------------------------------------

-- party_2 counter must be 1 at that point

------------------------------------------

-- party_2_button high for 2 cycle

party_2_button <= '1';

wait for clock_signal_period*2;

party_2_button <= '0';

-- select_party button high for 2 cycle

select_party <= '1';

wait for clock_signal_period*2;

select_party <= '0';

------------------------------------------

-- party_2 counter must be 2 at that point

------------------------------------------

-- party_2_button high for 2 cycle

party_2_button <= '1';

wait for clock_signal_period*2;

party_2_button <= '0';

-- select_party button high for 2 cycle

select_party <= '1';

wait for clock_signal_period*2;

select_party <= '0';

------------------------------------------

-- party_2 counter must be 3 at that point

------------------------------------------

-- party_2_button high for 2 cycle

party_2_button <= '1';

wait for clock_signal_period*2;

party_2_button <= '0';

-- select_party button high for 2 cycle

select_party <= '1';

wait for clock_signal_period*2;

select_party <= '0';

------------------------------------------

-- party_2 counter must be 4 at that point

------------------------------------------

-- party_2_button high for 2 cycle

party_2_button <= '1';

wait for clock_signal_period*2;

party_2_button <= '0';

-- select_party button high for 2 cycle

select_party <= '1';

wait for clock_signal_period*2;

select_party <= '0';

------------------------------------------

-- party_2 counter must be 5 at that point

------------------------------------------

wait for 100 ns;

wait;

end process;

END;